Цифровые микросхемы

Полупроводниковая электроника берет свое начало с 1948 г., когда группой разработчиков фирмы Bell был создан первый транзистор. Спустя 11 лет инженерами фирмы Texas Instruments была разработана первая микросхема, состоящая всего из шести транзисторов, а в 1971 г. ныне всемирно известная фирма Intel разработала первый 4-разрядный микропроцессор 4004, содержащий более 2000 транзисторов. В дальнейшем микроминиатюризапия электронных компонентов достигла таких темпов, что это послужило, поводом для весьма образного сравнения в журнале Sientific American (1982 г.): "Если бы авиапромышленность в последние 25 лет развивалась столь же стремительно, как и промышленность средств вычислительной техники, то сейчас самолет "Боинг-767" стоил бы 500 долларов и совершал облет земного шара за 20 минут, затрачивая при этом 5 галлонов топлива". Поразительные результаты, достигнутые в микроэлектронике, стали возможны благодаря не только новейшим полупроводниковым технологиям, но и огромному багажу схемотехнических решений, накопленному в течение десятилетий многомиллионной армией разработчиков. Несмотря на поражающие воображение количества транзисторов, собранных на крошечных полупроводниковых кристаллах, следует все-таки помнить, что они представляют собой наборы из простейших элементов, к рассмотрению которых мы и перейдем.

В зависимости от технологии изготовления интегральные микросхемы (ИМС) подразделяются на серии (семейства), различающиеся физическими параметрами базовых элементов и их функциональным назначением. Наибольшее распространение получили ИМС, изготовляемые по ТТЛ- и КМОП-технологиям. (ТТЛ — транзисторно-транзисторная логика с использованием биполярных транзисторов, КМОП — с использованием комплементарных МОП-транзисторов).

Первой была выпущена ТТЛ-серия SN74/SN54 (74 — коммерческая, 54 — для военных применений). Отечественным аналогом серии SN74 стала популярная в свое время серия 155. В 1967 г. дополнительно разработаны семейства SN74H/54H (High speed — быстродействующая, отечественные аналоги — серии 131 и 130) и SN74L/54L (Low power — маломощная, аналоги — серии 158 и 136).

В 1969 г. разработана серия SN74S/54S (серии 531 и 530), в 1971 г. — серия SN74LS/54LS (серии 555 и 533), в 1979 г. — серия SN74F/54F фирмы Fail-child (FAST — Fairchild's Advanced Schottky TTL, серия 1531), в 1980 г. — серия SN74ALS/54ALS (серия 1533), в 1982 г. — серия SN74AS/54AS (в обозначениях серий S — Schottky, LS — Low power Schottky, ALS — Advanced Low power Schottky, AS — Advanced Schottky, Advanced — усовершенствованная). Использование диодов с барьером Шотки позволило значительно повысить быстродействие ИМС за счет предотвращения глубокого насыщения транзисторов в ключевом режиме. Приятной для разработчика особенностью всех перечисленных серий является полное совпадение номеров выводов и обозначения типа для ИМС одинакового функционального назначения. Например, если SN7472 — JK-триггер, то обозначение 72 будет сопутствовать ему во всех сериях. Этот же принцип используется и в отечественных ИМС, хотя тип здесь обозначается буквами.

В библиотеке программы EWB используется только серия SN74. Редактирование параметров отдельных ИМС, к сожалению, невозможно. Для облегчения работы с библиотекой ниже приводится список отечественных аналогов серии SN74 (для краткости некоторые повторяющиеся символы опущены).

7400 155ЛАЗ 4 элемента 2И-НЕ (цифра 2 означает 2-входовой);

7402 155ЛЕ1 4 элемента 2ИЛИ-НЕ;

7406 155ЛНЗ 6 элементов НЕ с открытым коллектором;

7407 155ЛП9 6 буферных элементов с открытым коллектором;

7408 155ЛИ1 4 элемента 2И;

7409 155ЛИ2 4 элемента 2И с открытым коллектором;

7410 155ЛА4 3 элемента ЗИ-НЕ;

7412 155ЛА10 3 элемента ЗИ-НЕ с открытым коллектором;

7420 155ЛА1 2 элемента 4И-НЕ;

7422 155ЛА7 2 элемента 4И-НЕ с открытым коллектором;

7425 155ЛЕЗ 2 элемента 4И-НЕ со входом стробирования;

7426 155ЛА11 4 элемента 2И-НЕ с открытым коллектором;

7428 155ЛЕ5 4 элемента 2ИЛИ-НЕ;

7430 155ЛА2 Элемент 8И-НЕ;

7432 155ЛЛ1 4 элемента 2ИЛИ;

7437 155ЛА12 4 элемента 2И-НЕ с открытым коллектором;

7438 155ЛА13 4 элемента 2И-НЕ с открытым коллектором;

7440 155ЛА6 2 элемента 4И-НЕ с повышенной нагрузочной способностью;

7442 555ИД6 Дешифратор 4х10 (декодирование 4-разрядного двоичного числа в десятичное);

7451 155ЛР11 Элементы 2-2И-2ИЛИ-НЕ ( 2 элемента 2И, выходы которых подключены на кристалле ИМС к элементу 2ИЛИ-НЕ) и 2-ЗИ-2ИЛИ-НЕ (аналогично для 2-ЗИ);

7454 155ЛР13 Элемент 2-3-3-2И-4ИЛИ-НЕ (2 элемента 2И и 2 элемента ЗИ объединены через 4ИЛИ-НЕ);

7455 155ЛР4 Элемент 4-4И-2ИЛИ-НЕ (2 элемента 4И объединены через 2ИЛИ-НЕ) с возможностью объединения по ИЛИ (выходной каскад элемента 2ИЛИ-НЕ имеет дополнительные входы транзистора С — Collector и Е — Emitter, что и позволяет осуществить объединение по ИЛИ);

7472 155ТВ1 JK-триггер с элементом ЗИ на входах;

7474 155ТМ2 2 D-триггера;

7475 155ТМ7 4 D-триггера с прямыми и инверсными выходами;

7476 155ТВ7 2 JK-триггера;

7477 155ТМ5 4 D-триггера с прямыми выходами;

7486 155ЛП5 4 элемента Исключающее ИЛИ;

7490 155ИЕ2 4-разрядный асинхронный двоично-десятичный счетчик;

7492 155ИЕ4 4-разрядный асинхронный счетчик-делитель на 12;

7493 155ИЕ5 4-разрядный асинхронный двоичный счетчик;

74107 155ТВ6 2 JK-триггера с раздельной установкой нуля;

74109 155ТВ15 2 JK-триггера;

74112 155ТВ9 2 JK-триггера;

74113 155ТВ10 2 JK- триггера с предустановкой нуля или единицы;

74114 155ТВ11 2 JK-триггера с предустановкой нуля или единицы и общим обнулением;

74125 155ЛП8 4 буфера с тремя состояниями;

74126 155ЛП14 4 формирователя с тремя состояниями;

74134 155ЛА19 Элемент 12И-НЕ с тремя состояниями;

74138 155ИД7 Дешифратор-демультиплексор 3х8;

74139 155ИД14 2 дешифратора-демультиплексора 2х4;

74145 155ИД10 Двоично-десятичный дешифратор с открытым коллектором;

74148 155ИВ1 Шифратор приоритетов 8х3;

74150 155КП1 Селектор-мультиплексор 16х1;

74151 155КП7 Селектор-мультиплексор 8х1;

74152 155КП5 Селектор-мультиплексор 8х1;

74153 155КП2 2 селектора-мультиплексора 4х2;

74154 155ИДЗ Дешифратор-демультиплексор 4х16;

74155 155ИД4 2 дешифратора-мультиплексора 2х4;

74156 555ИД5 2 дешифратора-демультиплексора 2х4 с открытым коллектором;

74157 533КП16 4-разрядный селектор-мультиплексор 2х1;

74158 1533КП18 4-разрядный селектор-мультиплексор 2х1 с инверсией;

74160 155ИЕ9 4-разрядный синхронный двоично-десятичный счетчик;

74162 1533ИЕ11 4-разрядный синхронный десятичный счетчик;

74163 155ИЕ18 4-разрядный синхронный реверсивный двоично-десятичный счетчик;

74164 155ИР8 8-разрядный регистр сдвига с параллельными выходами;

74169 155ИЕ17 4-разрядный двоичный синхронный реверсивный счетчик;

74173 155ИР15 4-разрядный регистр с тремя состояниями;

74174 155ТМ9 6 D-триггеров; »

74175 155ТМ8 4 D-триггера;

74181 155ИПЗ 4-разрядное АЛУ;

74191 155ИЕ13 Синхронный реверсивный двоичный счетчик;

74194 155ИР11 4-разрядный универсальный регистр сдвига;

74195 155ИР12 4-разрядный регистр сдвига с параллельным вводом;

74198 155ИР13 8-разрядный универсальный регистр сдвига;

74240 155АПЗ 8 буферов с инверсией и тремя состояниями;

\

74241 155АП4 8 буферов с тремя состояниями;

74244 155АП5 2х4 буферов с тремя состояниями;

74251 155КП15 Селектор-мультиплексор 8х1 с тремя состояниями;

74253 155КП12 2 селектора-мультиплексора 4х1 с тремя состояниями;

74257 155КП11 4 селектора-мультиплексора 2х1 с тремя состояниями;

74258 155КП14 4 селектора-мультиплексора 2х1 с тремя состояниями и инверсией;

74273 155ИР35 8-разрядный регистр с установкой нуля;

74280 1533ИП5 9-разрядная схема контроля четности;

74283 155ИМ6 4-разрядный полный сумматор с ускоренным переносом;

74298 155КП13 4 2-входовых мультиплексора с запоминанием;

74365 155ЛП10 6 повторителей с управлением по входам и тремя состояниями;

74367 155ЛП11 6 повторителей с раздельным управлением по входам и тремя состояниями;

74373 155ИР22 8-разрядный буферный регистр с тремя состояниями и потенциальным управлением;

74374 155ИР23 8-разрядный буферный регистр с тремя состояниями и импульсным управлением;

74377 155ИР27 8-разрядный регистр с разрешением записи.

Ссылки в этом перечне на ИМС других серий вызвано их отсутствием в серии 155, однако здесь это не имеет существенного значения, поскольку речь идет только о выяснении функционального назначения выводов.

Цифровые ИМС КМОП-серии получили название от своего базового элемента, в котором используется так называемая комплементарная пара из двух МОП-транзисторов различной проводимости. Такие ИМС характеризуются малым потреблением мощности в статическом режиме (0,02...! мкВт на вентиль), большим диапазоном питающих напряжений (3.18 В), высоким входным сопротивлением (до десятков ТОм), большой нагрузочной способностью, незначительной зависимостью характеристик от температуры, малыми размерами транзисторов в интегральном исполнении и, как следствие, более высокой степенью интеграции по сравнению с ТТЛ-микросхемами.

Первые ИМС по КМОП-технологии разработаны фирмой RCA в 1968 г. Эта серия имела название CD4000 (отечественные аналоги — серии 164 и 176), затем последовали серии CD4000A, CD4000B (отечественные аналоги — 564, 561 и 1561, а также МС14000А и МС14000В фирмы Motorola) и 54НС фирмы National Semiconductor в 1981 г. (отечественный аналог — серия 1564). В программе EWB в качестве библиотечных используюся ИМС фирмы RCA, большинство которых приведено в следующем перечне:

4001 561ЛЕ5 4 элемента 2ИЛИ-НЕ;

4002 561ЛЕ6 2 элемента 4ИЛИ-НЕ;

4011 561ЛА7 4 элемента 2И-НЕ;

4012 561ЛА8 2 элемента 4И-НЕ;

4013 561ТМ2 2 D-триггера;

4015 561ИР2 2 4-разрядных сдвиговых регистра;

4023 561ЛА9 3 элемента ЗИ-НЕ;

4025 1561ЛЕ10 3 элемента ЗИЛИ-НЕ;

4028 561ИД1 двоично-десятичный дешифратор;

4030 561ЛП2 4 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ;

4040 1561ИЕ20 12-разрядный двоичный счетчик;

4066 561КТЗ 4 переключателя (цифрового или аналогового сигнала);

4070 1561ЛП14 4 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ;

4081 1561ЛИ2 4 элемента 2И.

Приведем систему обозначений входов и выходов простейших логических элементов, используемых в программе EWB. Обозначения для ТТЛ-серии приводятся в первых круглых скобках, для КМОП — во вторых, при одинаковых обозначениях — без скобок:

Вывод для питания — (Ucc), (Udd);

Общий вывод — (GND), (Uss);

Вывод не подключен — NC;

Входы—(А, В, С...),(!);

Выходы — (Y), (О);

Вход стробирования — (G).

Приведем пример обозначения последовательности выводов для 2-входовых логических элементов:

(1А 1В 1Y, 2А 2В 2Y, ЗА 3В 3Y, 4А 4В 4Y), (II 12 01,13 14 02,15 16 03,17 18 04).

Для более сложных ИМС определение функционального назначения их выводов целесообразно проводить путем сопоставления с отечественными аналогами [4—10].

Рассмотрим так называемые базовые элементы, из которых набираются самые сложные цифровые ИМС.

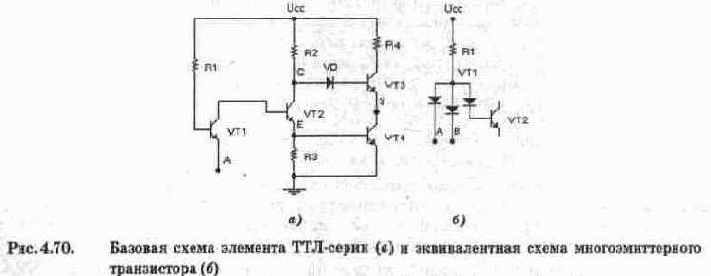

Схема базового элемента (вентиля) ТТЛ-серии показана на рис. 4.70, а. Она содержит три основных каскада: входной на транзисторе VT1, фазорасщепительный на транзисторе VT2 с возможностью реализации на нем функции ИЛИ и выходной усилитель на транзисторах VT3 и VT4 [49].

В качестве транзистора VT1 используется многоэмиттерный транзистор, отсутствующий в библиотеке EWB. Принцип действия входного каскада легко понять, если переходы база-эмиттеры представить в виде диодов, как показано на рис. 4.70, б. Тогда очевидно, что если входные диоды (входы А, В) подключены к шине с высоким напряжением (4...5 В), то ток резистора R1 потечет через коллекторный диод в базу транзистора VT2. Если же хотя бы один из входных диодов подключен к земляной шине или к шине с низким напряжением, то таким же образом окажется подключенным и резистор R1. На базе транзистора VT1 при этом будет низкое напряжение (превышающее входное на величину напряжения база-эмиттер) и базовый ток транзистора VT2 станет равным нулю.

Таким образом, при высоких напряжениях на обоих входах на коллекторе транзистора VT1 также будет высокое напряжение; если же хотя бы на один из входов подано близкое к нулю напряжение, то на коллекторе VT1 установится низкое напряжение, а это означает, что входной транзистор выполняет логическую функцию И.

Фазорасщепляющий каскад выполнен на транзисторе VT2 и резисторах R2, R3 примерно равного сопротивления (около 0,25...0,33 от R1). При этом насыщение транзистора VT2 достигается уже при достаточно малом коэффициенте усиления тока. Когда на все логические входы схемы подано высокое напряжение, через переход база-коллектора транзистора VT1 в базу VT2 подается управляющий ток, в результате чего VT2 открывается. При этом напряжение в точке Е может возрасти только до напряжения база-эмиттер транзистора VT4, а напряжение в точке С (на коллекторе VT2) снизится до значения, равного сумме напряжений открытых диода VD и транзистора VT3. Если хотя бы на один из логических входов подается низкое напряжение (сигнал логического нуля), то транзистор VT1 открывается, отключая управляющий базовый ток транзистора VT2, в результате чего VT2 закрывается и через резисторы R2, R3 протекает только ток утечки, поэтому напряжения в точках Е и С близки к нулю и Ucc соответственно. Логическая функция ИЛИ может быть реализована при параллельном соединении двух или более подобных фазорасщепи-тельных каскадов (в точках С и Е).

Основным транзистором выходного каскада является транзистор VT4. Когда на входы А, В (рис. 4.70, б) подано высокое напряжение, транзисторы VT2 и VT3 открыты. В этом случае напряжение в точке С будет равно, как указано выше, напряжению двух открытых р— га-переходов. Если временно исключить из рассмотрения транзистор VT4 и рассматривать только цепь, содержащую диод VD и транзистор VT3, то напряжение в точке S будет ниже напряжения в точке С на величину, равную напряжению на двухр—га-переходах. При этом напряжение на базе транзистора VT4 будет достаточным (именно за счет диода VD) для поддержания его в открытом состоянии, т.е. на выходе S будет действовать напряжение, равное напряжению насыщения транзистора VT4 (сигнал логического нуля).

Если хотя бы на один из входов вентиля А или В подано низкое напряжение, то транзисторы VT2 и VT4 закрыты. Через резистор R2 течет только ток утечки транзистора VT2, поэтому напряжение в точке С близко к напряжению питания Vcc, а потенциал в точке S ниже потенциала С на величину падения напряжения на двух открытых переходах. Падением напряжения на резисторе R2 от базового тока транзистора VT4 можно пренебречь. Таким образом, при наличии хотя бы на одном из входов вентиля низкого напряжения его выходное напряжение будет ниже напряжения питания на падение напряжения на двух р—га-переходах. В различных сериях ТТЛ используются разные схемы выходных каскадов, однако всегда между шиной Ucc и выходом S имеются два последовательно включенных р—га-перехода. Резистор R4 служит для защиты транзистора VT3 при закорачивании выхода S на "землю".

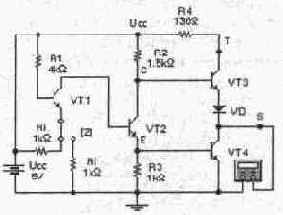

Рис. 4.71. Схема базового элемента серии 54/74

Базовый элемент серии 54/74 (155) (рис. 4.71) немного отличается от рассмотренного (рис. 4.70). Основное отличие заключается в том, что диод VD включен в эмиттерную, а не в базовую цепь транзистора. На рис. 4.71 показан также подключенный к выходу мультиметр и имитатор входного сигнала, выполненный на ключе Z. В положении ключа, показанном на рисунке, на входе формируется сигнал логической единицы. При переводе ключа в другое положение вход вентиля подключается через резистор Ri к общей шине, в результате чего на входе вентиля формируется сигнал логического нуля.

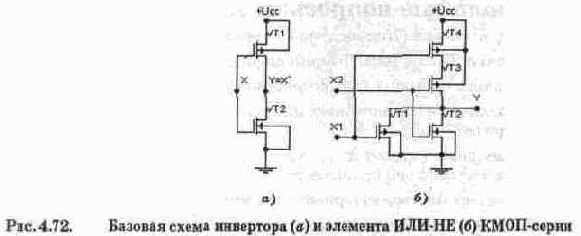

Рассмотрим теперь базовые элементы ИМС КМОП-серии. Простейшим элементом этой серии является КМОП-инвертор, схема которого показана на рис. 4.72, а. Она составлена из КМОП-транзисторов разного типа проводимости. Транзистор га-типа подключен истоком к нулевому потенциалу, транзистор р-типа — к положительной шине источника питания. Схема реализует логическую операцию НЕ и обеспечивает работу в режиме положительной логики. В таком режиме работают большинство ИМС КМОП-серий.

Для реализации функции ИЛИ-НЕ (рис. 4.72, б) используется параллельное включение МОП-транзисторов га-типа и последовательное (ярусное) включение транзисторов р-типа. Кроме того, каждый из входных транзисторов га-типа связан по затвору с транзистором р-типа. Для реализации функции И-НЕ (рис. 4.73) параллельно включаются транзисторы р-типа и последовательно — транзисторы га-типа. При подаче на вход схемы ИЛИ-НЕ сигнала Х1высокого уровня, откроется транзистор VT1 и закроется VT4. В результате на выходе схемы формируется низкий уровень напряжения. При подаче на оба входа (XI и Х2) сигналов низкого уровня транзисторы VT1 и VT2 закрываются, но открываются транзисторы VT3 и VT4, в результате чего на выходе схемы напряжение будет близко к напряжению питания Ucc. Таким образом, перезаряд емкости нагрузки, подключаемой между выходным зажимом Y и общей шиной, всегда осуществляется через открытый транзистор р-или га-типа, что повышает быстродействие схемы.

Мощность, потребляемая схемой на КМОП-транзисторах, расходуется в основном во время переходного процесса на заряд выходных паразитных емкостей схемы и собственных емкостей транзистора. Поэтому с увеличением частоты переключения, а также при увеличении выходной эквивалентной емкости потребляемая мощность возрастает в соответствии с выражением Р,„„=2С-Г-Щ„ где С — эквивалентная емкость нагрузки; F — рабочая частота; Це — напряжение источника питания.

В статическом режиме потребляемая мощность определяется напряжением питания и токами утечки закрытого МОП-транзистора. Для уменьшения мощности, потребляемой в динамическом режиме, необходимо в первую очередь снижать емкость нагрузки.

Минимальное напряжение питания схемы на КМОП-транзисторах определяется напряжением отпирания р-канального транзистора, так как оно больше, чем напряжение отпирания ге-канального транзистора. Естественно, что напряжение питания выбирается больше напряжения отпирания. Это обеспечивает схеме на КМОП-транзисторах высокую помехоустойчивость и быстродействие.

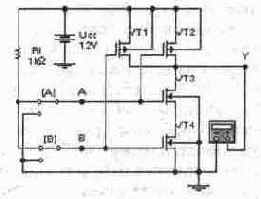

Схема И-НЕ на рис. 4.73 содержит имитатор входного сигнала на ключах А, В и мультиметр для проверки правильности функционирования схемы. В положении переключателей, показанных на схеме, на входы А, В подаются сигналы логической единицы. При этом транзисторы VT1, VT2 будут закрыты, а транзисторы VT3, VT4 — открыты и на выходе Y мультиметром будет фиксироваться низкий уровень сигнала логического нуля. Достаточно один из выключателей перевести в другое положение и один из двух нижних транзисторов закроется, при этом на выходе Y будет фиксироваться высокий уровень сигнала логической единицы, что и соответствует логике работы элемента И-НЕ.

Рис. 4.73. Схема базового элемента И-НЕ КМОП-серии

Контрольные вопросы и задания

1. Когда и где были созданы первая микросхема и первый микропроцессор?

2. Что из себя представляют ТТЛ- и КМОП-серии цифровых ИМС?

3. Что позволило радикально повысить быстродействие ТТЛ-серии?

4. В чем заключается различие в обозначениях цифровых ИМС зарубежного и отечественного производства?

5. Какое основное преимущество имеют цифровые КМОП-микросхемы по сравнению с ТТЛ и на каких частотах оно проявляется?

6. Какие функции выполняет многоэмиттерный транзистор в ИМС ТТЛ-серии?

7. Из описания процесса формирования на выходе S сигнала логического нуля в схеме вентиля на рис. 4.70, а не совсем ясно, в каком состоянии при этом находится транзистор VT3 — в открытом или закрытом. Для проверки необходимо при логической единице на входах А, В измерить с помощью мультиметра напряжение на коллекторе VT3, предварительно убедившись, что на выходе S сигнал логического нуля. Если это напряжение равно Ucc=+5 В, то это означает, что через резистор R4 ток не течет и, следовательно, транзистор VT3 закрыт. Если это так, попытайтесь объяснить, почему?

8. Проверьте правильность функционирования схемы на рис. 4.73.