Регистры

Основное назначение регистров — хранение и преобразование многоразрядных двоичных чисел. Регистры наряду со счетчиками и запоминающими устройствами являются наиболее распространенными устройствами цифровой техники. При сравнительной простоте регистры обладают большими функциональными возможностями. Они используются в качестве управляющих и запоминающих устройств, генераторов и преобразователей кодов, счетчиков, делителей частоты, узлов временной задержки [7, 8]. Элементами структуры регистров являются синхронные триггеры D- или JK-типа с динамическим или статическим управлением. Одиночный триггер может запоминать (регистрировать) один разряд (бит) двоичной информации. Такой триггер можно считать одноразрядным регистром. Занесение информации в регистр называют операцией ввода или записи. Выдача информации к внешним устройствам характеризует операцию вывода или считывания. Запись информации в регистр не требует его предварительного обнуления.

Понятие "весовой коэффициент" к разрядам регистра в отличие от счетчика неприменимо, поскольку весовая зависимость между отдельными разрядами целиком определяется записанной в регистр информацией. По этой причине на условных изображениях регистров нумерация информационных входов и выходов наносится подряд.

Все регистры в зависимости от функциональных свойств подразделяются на две категории — накопительные (регистры памяти, хранения) и сдвигающие. В свою очередь, сдвигающие регистры делятся по способу ввода и вывода информации на параллельные, последовательные и комбинированные (параллельно-последовательные и последовательно-параллельные), по направлению передачи (сдвига) информации — на однонаправленные и реверсивные.

Наиболее простыми регистрами являются регистры памяти. Их назначение — хранение двоичной информации небольшого объема в течение короткого промежутка времени. Эти регистры представляют собой набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Ввод (запись) и вывод (считывание) информации производится параллельным кодом. Ввод обеспечивается тактовым импульсом, с приходом очередного тактового импульса записанная информация обновляется. Считывание производится в прямом или в обратном коде (в последнем случае с инверсных выходов).

Регистры хранения представляют собой наборы триггеров с независимыми информационными входами и обычно общим тактовым входом. В таком качестве используются синхронные триггеры, составленные из микросхем, содержащих в одном корпусе несколько самостоятельных триггеров, например К155ТМ8 (74175), К155ТМ9 (74179) и другие, которые можно рассматривать как 4—6-разрядные регистры памяти. Наращивание разрядности регистров памяти достигается добавлением нужного числа триггеров, тактовые входы которых подсоединяют к шине синхронизации.

Рис. 9.40. Схема включения регистра 74173

Регистр К155ИР15 (74173) является библиотечным компонентом EWB и может служить примером устройства хранения с тремя выходными состояниями. Схема его включения приведена рис. 9.40. Отметим крайне неудачное расположение выводов регистра 74173 и их несоответствие оригиналу [7, 8]. Как видно из рис. 9.40, К155ИР15 — четырехразрядный регистр. Он имеет выходы 1Q...4Q с третьим Z-состоянием (при сигнале 1 на выводах G2, G1), а его входы 1D...4D снабжены логическими элементами разрешения записи путем подачи логического 0 на входы М, N (в EWB ошибочно показаны прямыми). Используется регистр как четырехразрядный источник кода, способный обслуживать непосредственно шину данных цифровой системы.

Загрузка информации в регистр производится синхронно с положительным перепадом тактового импульса, если на входах М, N присутствуют напряжения низкого уровня. Если на одном из этих входов напряжение высокого уровня, после прихода положительного тактового перепада в регистре должны остаться прежние данные. Вход сброса CLR имеет высокий активный уровень. Если на входы G2, G1 подано напряжение активного низкого уровня, данные, содержащиеся в регистре, отображаются на выходах 1Q...4Q, присутствие хотя бы одного напряжения высокого уровня на входах разрешения G2 и G1 вызывает Z-состояние (размыкание) для выходных линий. При этом данные из регистров шину данных систем не проходят, выходы регистра не влияют на работу других аналогичных выходов, присоединенных к проводникам шины. На работу входов сброса CLR и тактового С смена уровней на входах разрешения влияния не оказывает.

Регистр К155ИР15 потребляет ток 72 мА и имеет тактовую частоту до 25 МГц; вариант 74LS173 потребляет ток 30 мА, его тактовая частота 30 МГц. Режимы работы генератора в схеме на рис. 9.40 и некоторые кодовые комбинации показаны на рис. 9.41.

Вторым наиболее распространенным классом регистров являются регистры сдвига, которые отличаются большим разнообразием как в функциональном отношении, так и в отношении схемных решений и характеристик. Регистры сдвига, помимо операции хранения, осуществляют преобразование последовательного двоичного кода в параллельный, а параллельного — в последовательный, выполняют арифметические и логические операции, служат в качестве элементов временной задержки. Своим названием они обязаны характерной для этих устройств операции сдвига. С приходом каждого тактового импульса происходит перезапись (сдвиг) содержимого триггера каждого разряда в соседний разряд без изменения порядка следования единиц и нулей. При сдвиге информации вправо после каждого тактового импульса бит из более старшего разряда сдвигается в младший, а при сдвиге влево — наоборот.

На отечественных схемах символом регистра служат буквы RG. Для регистров сдвига указывается также направление сдвига: > — вправо; < — влево; <-> — реверсивный (двунаправленный).

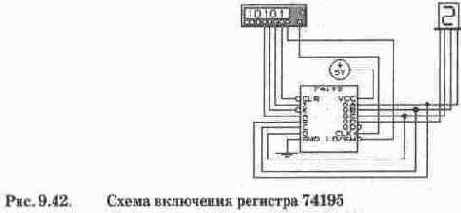

Работу регистра сдвига рассмотрим на примере библиотечного регистра 74195 (К155ИР12), схема включения которого показана на рис. 9.42. ИМС 74195 — быстродействующий регистр для выполнения операций сдвига, счета, накопления и взаимного параллельно-последовательного преобразования цифровых слов. Через вход LD/SH загружаются параллельные данные и производится их сдвиг вправо. Если на этом входе присутствует напряжение высокого уровня, через входы первого триггера J и К в регистр вводятся последовательные данные. Вход J имеет высокий активный уровень, вход К — низкий; если эти входы соединить, получим простой D-вход. Данные сдвигаются в направлении от QA к QB, QC, а затем к QD после каждого положительного перепада на тактовом входе CLK.

Если на входе LD/SH присутствует напряжение низкого (активного) уровня, все четыре триггера регистра запускаются одним тактовым перепадом (от низкого уровня к высокому). Тогда данные от параллельных входов A...D передаются на соответствующие выходы QA...QD. Сдвиг данных влево обеспечивается в схеме, где каждый выход Qn соединен внешней перемычкой со входом Dni, т.е. схема включения на рис. 9.42 соответствует только режиму приема и хранения данных.

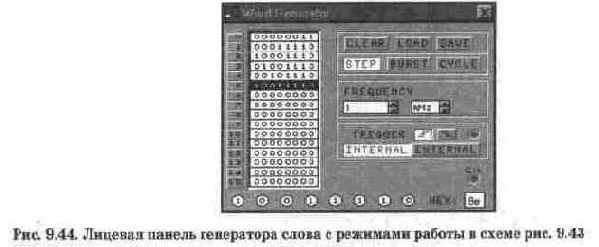

Схема включения ИМС в режиме сдвига показана на рис. 9.43, режимы работы генератора слова — на рис. 9.44. Для режима сдвига напряжение на входе LD/SH надо зафиксировать на высоком уровне. Из-за того, что все операции в регистре ИР12 строго синхронны и запускается он фронтом импульса, логические уровни на входах J, К, Dn, LD/SH можно произвольно изменять до прихода фронта запуска. Низким уровнем на входе CLR всем выходным сигналам присваивается низкий уровень.

Напряжение низкого уровня на входе CLR означает также запрет на действие тактового импульса CLK, для правильного сброса данных надо выбрать момент, когда на входе CLK присутствует напряжение низкого уровня.

Контрольные вопросы и задания

1. Что такое регистр, какие функции он может выполнять?

2. Назовите типы регистров и их возможные применения.

3. Проведите моделирование регистра 74133 по схеме на рис. 9.40. При моделировании необходимо выбрать с помощью генератора слова двоичные комбинации, которые позволяют проверить все режимы его работы. Целесообразно также составить так называемую таблицу состояния, напоминающую таблицу истинности [7, 8].

4. Проведите моделирование регистра 74195 в режиме приема данных (рис. 9.42).

5. Для приведенной на рис. 9.43 схемы исследуйте следующие режимы сдвига [7]:

1 — сдвиг и установка по первому каскаду (JK=11); 2 — сдвиг и сброс по первому каскаду (JK=00); 3 — сдвиг и переключение первого каскада (JK=10); 4 — сдвиг и хранение в первом каскаде (JK=01). При этом, как указывалось выше, CLR=1, LD/SH=1, состояние входа А безразлично.