Арифметико-логическое устройство

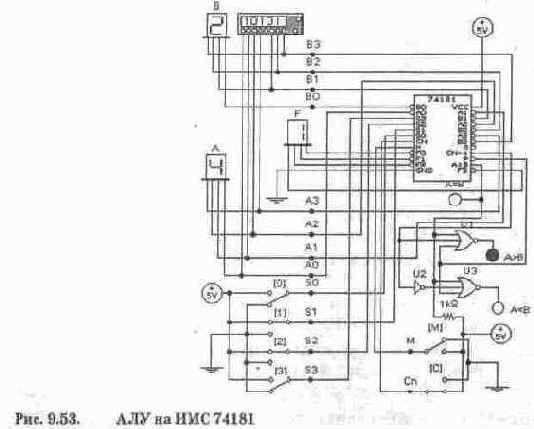

В разд. 9.2 уже упоминалась ИМС арифметико-логического устройства (АЛУ) 74181 (К155ИПЗ) в связи с возможностью использования ее в качестве четырехразрядного сумматора. Там же указывалось, что эта ИМС обеспечивает 32 режима работы АЛУ в зависимости от состояния управляющих сигналов на входах М, SO...S3. Показанная на рис. 9.53 схема на базе этой ИМС позволяет оперативно реализовать все упоминавшиеся режимы.

Возможные режимы задаются с помощью переключателей О, 1, 2, 3 для подачи сигналов 0 ("земля") или 1 (+5 В) на входы управления SO, SI, S2, S3. В положении переключателя М, показанном на рис. 9.53 (сигнал 0 на входе М), выполняются 16 арифметических операций (16 комбинаций сигналов SO...S3) с учетом переноса по входу Сп (переключатель С в показанном на рис. 9.53 положении) или без учета переноса (сигнал 0 на входе Сп переключателя С). При переводе ключа М в другое положение (на входе М сигнал 1) выполняются 16 логических операций, задаваемых теми же переключателями 0... 3.

Значения четырехразрядных операндов А и В задаются с помощью генератора слова и в шестнадцатеричном коде отображаются на алфавитно-цифровых индикаторах. На выходах FO...F3 результат суммирования отображается индикатором F. При коде 1111 на этих выходах и при равенстве операндов выход А=В переводится в единичное состояние. Поскольку этот выход представляет собой каскад с открытым коллектором, то на него подается питание +5 В через резистор 1 кОм. Выход А=В совместно с выходом переноса CN+4 и выходом Р подтверждения переноса используются для формирования признаков А>В и А<В с помощью дополнительных логических элементов Ul, U2, U3.

Изменяя состояния сигналов на управляющих входах, можно промоделировать большинство функций АЛУ, используемых в микропроцессорах. Приведем перечень этих функций.

Логические функции (на входе М сигнал 1); выполняются поразрядно, переносы не учитываются.

Код 0000 на входах S3, S2, SI, SO; при этом выполняется логическая функция А' — данные со входов А передаются на выходы F с инверсией, может быть использована в команде СМА (здесь и далее используется мнемоника команд микропроцессоров семейства 80хх фирмы Intel).

0001 — (А+В)'— поразрядная операция ИЛИ с инверсией над операндами А и В;

0010 — A'B — операция И инвертированного операнда А и операнда В;

ООН — 0 — нет операции;

0100 — (АВ)' — операция И с инверсией;

0101 — В'— инверсия операнда В;

ОНО — АФВ — операция Исключающее ИЛИ, команда XRA;

0111 — АВ'— операция И над операндами А и инверсией В;

1000 — А'+В — операция ИЛИ над инверсией А и операндом В;

1001 — (А+В)' — операция ИЛИ с инверсией;

1010 — В — передача на выход операнда В;

1011 — АВ — операция И, команда ANA;

1100—1;

1101 — А+В' — операция ИЛИ над инверсией В и операндом А;

1110 — А+В — операция ИЛИ, команда ORA;

1111 — А — передача на выход операнда А.

Арифметические операции (М=0) без переноса (Сп=1) и с переносом (Сп=0, данные приводятся в круглых скобках):

0000 — А — передача на выход операнда (А+1 — суммирование операнда с 1 переноса, команда инкремента).

0001 — А+В — операция суммирования без учета переноса, команда ADD ((A+B)+1 — суммирование с учетом переноса, команда ADC);

0010 — А+В' — операция суммирования операнда А с инверсией операнда В без учета переноса ((А+В')+1 — то же, но с учетом переноса);

ООН — -1 (0);

0100 — А+АВ' (А+(АВ)'+1). Далее мы от комментариев воздержимся в надежде, что из вышеизложенного все и так очевидно;

0101 — (А+В)+АВ'((А+В)+АВ'+1);

ОНО — А-В-1, команда SBB (А-В, команда SUB);

01Н—АВ'-1((АВ)');

1000 — А+АВ(А+В+1);

1001 — А+В, команда ADD (A+B+1);

1010 — (А+В')+АВ ((А+В')+АВ+1);

lOH-AB-l(AB);

1100 — А+А(А+А+1);

1101 — (А+В)+А((А+В)+А+1);

1110 — (А+В')+А ((А+В')+А+1);

1111-А-1(А).

Контрольные задания

1. Проведите моделирование всех перечисленных выше режимов АЛУ (рис. 9.53), предварительно составив неповторяющиеся комбинации на выходе генератора слова.

2. Дополните операции без комментариев описанием выполняемых ими функций.

3. Проанализируйте систему команд микропроцессора 18080 (КР580ИК80) и возможность использования в них логических функций и арифметических операций ИМС 74181.