Устройство контроля четности

9.7. Устройство контроля четности

Операция контроля четности двоичных чисел позволяет повысить надежность передачи и обработки информации. Ее сущность заключается в суммировании по модулю 2 всех разрядов с целью выяснения четности числа, что позволяет выявить наиболее вероятную ошибку в одном из разрядов двоичной последовательности. Например, если при передаче кода 1001 произойдет сбой во втором разряде, то на приемном пункте получим код 1101 — такую ошибку определить в общем случае затруднительно. Если же код относится к двоично-десятичному (8-4-2-1), то ошибку легко обнаружить, поскольку полученный код (десятичный эквивалент — число 13) не может в принципе принадлежать к двоично-десятичному.

Обнаружение ошибок путем введения дополнительного бита четности происходит следующим образом. На передающей стороне передаваемый код анализируется и дополняется контрольным битом до четного или нечетного числа единиц в суммарном коде. Соответственно суммарный код называется четным или нечетным. В случае нечетного кода дополнительный бит формируется таким образом, чтобы сумма всех единиц в передаваемом коде, включая контрольный бит, была нечетной. При контроле четности все, естественно, наоборот. Например, в числе 0111 число единиц нечетно. Поэтому при контроле нечетности дополнительный бит должен быть нулем, а при контроле четности — единицей. На практике чаще всего используется контроль нечетности, поскольку он позволяет фиксировать полное пропадание информации (случай нулевого кода во всех информационных разрядах). На приемной стороне производится проверка кода четности. Если он правильный, то прием разрешается, в противном случае включается сигнализация ошибки или посылается передатчику запрос на повторную передачу.

Схема формирования бита четности [8] для четырехразрядного кода показана на рис. 9.25. Она содержит четыре элемента Исключающее ИЛИ, выполняющих функции сумматоров по модулю 2 (без переноса) и состоит из трех ступеней. На первой ступени попарно суммируются все биты исходного кода на входах А, В, С, D. На второй ступени анализируются сигналы первой ступени и устанавливается четность или нечетность суммы входного кода. На третьей ступени полученный результат сравнивается с контрольным сигналом на входе Е, задающим вид используемого контроля, в результате чего на выходе F формируется пятый дополнительный бит четности, сопровождающий информационный сигнал в канале передачи.

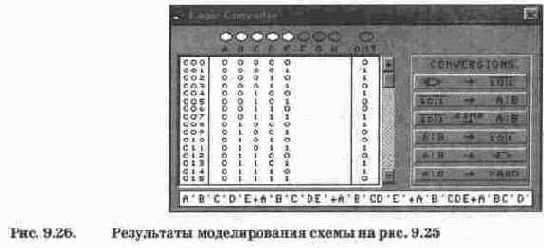

Результаты моделирования формирователя показаны на рис. 9.26 в виде таблицы истинности из 32 возможных двоичных комбинаций и булева выражения (из 32 комбинаций на рис. 9.26 видны только первые 16, остальные просматриваются с помощью линейки прокрутки). Для просмотра составляющих булева выражения необходимо мышью поместить курсор в дополнительный дисплей и передвигать его клавишами управления курсором.

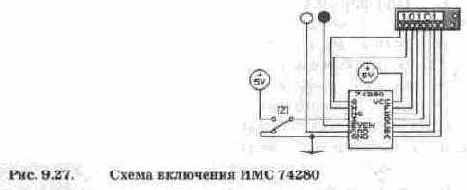

В библиотеке программы EWB схема проверки на четность и нечетность представлена ИМС 74280 (аналог — К555ИП5), схема ее включения показана на рис. 9.27. ИМС 74280 имеет 9 входов (A, B...I) и два выхода (EVEN, ODD), один из которых — инверсный. Вход I используется для управления видом контроля (0 — контроль четности, 1 — контроль нечетности) и управляется переключателем Z (управляется с клавиатуры одноименной клавишей). Вывод NC — not connection — пустой, т.е. внутри ИМС к нему ничего не подключено.

Правильность функционирования схемы на рис. 9.27 проверяется с помощью генератора слова, при этом тип контроля (четности или нечетности) выбирается переключателем Z; на входы рассматриваемого устройства подаются различные двоичные комбинации; состояние выходов ИМС контролируется подключенными к ним светоиндикаторами (логическими пробниками).

Контрольные вопросы и задания

1. Какое назначение имеют формирователи кода четности, где они могут быть использованы?

2. Какая форма контроля четности чаще всего используется на практике, в частности, в Вашем компьютере, если в нем установлены модули ОЗУ с нечетным числом микросхем (см. разд. 5.12)?

3. Из представленных на экране логического преобразователя данных (рис. 9.26) выберите комбинации, относящиеся к контролю четности и нечетности, а также соответствующие им слагаемые булева выражения.

4. Проверьте правильность функционирования схемы на рис. 9.27, подавая на входы двоичные комбинации с генератора слова.